|

|||||||||||||||||||||||||||||||||||||||||||||||||

| Nederlands | French |

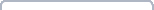

SEGGER Instruction Tracing with SEGGER J-Link/J-Trace and Atollic TrueStudioHilden, Germany – July 10th, 2013 – SEGGER’s J-Trace debug probe facilitates ETM instruction trace within Atollic TrueStudio (v4.1 and newer). If the target microcontroller has an internal trace buffer (ETB), this limited tracing also works when using any one of the J-Link/J-Trace models available from SEGGER.ETM instruction trace allows the developer to look at the history of program execution. This is useful, for example, when a program crash is caused by an unexpected jump. In this case the developer can track back to where the program execution left the intended flow of the program. “By adding instruction trace, Atollic’s TrueStudio becomes one of the top players in the tool-chain market for embedded systems”, says Dirk Akemann, Marketing Manager of SEGGER. “SEGGER is the leading provider of debug probes and the combination of Atollic TrueSTUDIO and J-Trace provides engineers market-leading debugging and programming tools”, says Magnus Unemyr, Atollic. “Additionally, the SEGGER debug probes enable the Atollic TrueVERIFIER unit test system, and the Atollic TrueANALYZER test quality measurement system, to test the embedded application in the target board, thus providing developers with an unrivalled tool solution for improving the software quality.” J-Link supports multiple CPU families, such as ARM 7, 9, 11, Cortex-M0, M0+, M1, M3, M4, R4, A5, A8, A9 as well as Renesas RX610, 620, 62N, 62T, 630, 631, 63N; there is typically no need to buy a new J-Link or new license when switching to a different CPU family or tool-chain. SEGGER is also continuously adding support for additional cores, which in most cases, only requires a software/firmware update. Unlimited free updates are included with even the baseline model of the J-Link. SEGGER is excited to continue advanced development of its cutting edge embed

ded tool solutions to be utilized with pretty much any development environment you choose. All J-Links are fully compatible to each other, so an upgrade from a lower-end model to a higher-end model is a matter of a simple plug-and-play.

10-07-2013 |

|

|

|||||||

|

|

|

|

|

|

||

Read more

Read more